| Services and Modeling for Embedded Software Development |

|---|

Application Note 1. Issue 2

May 2010

Copyright © 2008, 2010 Embecosm Limited

| The document entitled " Building a Loosely Timed SoC Model with OSCI TLM 2.0 " by Jeremy Bennett of Embecosm is licensed under a Creative Commons Attribution 2.0 UK: England & Wales License. See the Legal Notice for details. |

Table of Contents

Or1ksimExtSC Wrapper Module

UartSC Module Class

TermSC Module Class

Or1ksimIntrSC Module Class

The Open SystemC Initiative (OSCI) has issued the second version of its standard for Transaction Level Modeling (TLM) in June 2008 [6]. This defines an interface for writing high level software models of hardware. An updated version (TLM 2.0.1) was released in July 2009.

The OSCI standard is comprehensive. As well as a powerful general purpose interface, it defines a number of convenience components to facilitate adoption of the technology.

This application note provides an introductory tutorial on using TLM 2.0 for loosely timed models—ideally suited for early development of embedded software. It demonstrates through a practical case study the development of a complete SoC, capable of running a modern Linux 2.6 kernel, using the TLM 2.0 convenience components.

One of the most important components in any SoC system model is the processor core Instruction Set Simulator (ISS). This application note demonstrates how to wrap an existing ISS to provide a TLM 2.0 compliant interface.

This application note is the first in a series from Embecosm (www.embecosm.com), providing case studies in OSCI TLM 2.0 use. The objective is to provide an introduction to TLM 2.0 within a practical context. Examples are provided throughout, based on open source components, which are freely reusable under the GNU General Public License.

Issue 2 of the application note is based on TLM 2.0.1. The wrapping of the ISS is extended to cover modeling of the JTAG interface and its connection to the GNU debugger, GDB.

To aid in understanding how the components fit together, this issue includes UML class and sequence diagrams, showing the relationships and interaction between classes.

The examples have been reworked to make them easier to build. In particular the example OpenRISC programs are now also built automatically.

Finally, Robert Günzel (see Section 1.4), as well as making a number of well informed suggestions for improvements which I have adopted, has written a paper on using this application note under Mac OS (Appendix B).

SystemC represents a challenge to engineers, because it bridges the divide between the worlds of hardware and software. These are two distinct disciplines, the languages of hardware design such as Verilog and VHDL are very different in philosophy to the languages of software development such as C++ and Java. Yet both are brought together in the world of the System on Chip SoC, where large embedded software systems must run on complex silicon chips often containing multiple processor cores of different architectures.

This application note is aimed at any engineer intending to bridge the gap between hardware and software. It recognizes that the reader will most likely be expert in only one of these. Explanation is provided throughout of both the hardware ideas and software ideas being covered.

The reader is assumed to have basic programming familiarity with C and C++ and the key concepts of object oriented programming: classes and instances of classes. A basic understanding of system level hardware design and the construction of SoC from components linked by buses (or on-chip networks).

Familiarity with SystemC is assumed. The user guide supplied with SystemC provides a good introduction [7].

The OSCI TLM 2.0 standard represents a significant advance in standardizing the creation of fast models of hardware.

However the OSCI reference implementation lacks training material and examples to introduce new users to the technology.

This series of Embecosm Application Notes was prompted by a customer requesting assistance in porting an existing ISS to the TLM 2.0 standard. This is the first application note in the series. Further Embecosm Application Notes, addressing different aspects of TLM 2.0 are available from the Embecosm website at www.embecosm.com.

I am indebted to Dipl Ing Robert Günzel of the Department of Integrated Circuit Design at the Technische Universität Braunschweig, Germany, who made a number of suggestions for improvements (which I have adopted) and provided the instructions for Mac OS (see Appendix B).

The development of SystemC as a standard for modeling hardware started in 1996. Version 2.0 of the proposed standard was released by the Open SystemC Initiative (OSCI) in 2002. In 2006, SystemC became IEEE standard 1666-2005 [5].

OSCI has several groups working on supplementary standards. One of these is the TLM Working Group. It proposed its first standard for transaction level modeling in 2005. Two drafts for version 2.0 were released in 2006 and 2007. The version 2.0 standard issued in June 2008, with a minor update (2.0.1) issued in June 2009 [6].

Most software languages are not particularly suited to modeling hardware systems[1]. SystemC was developed to provide features that facilitate hardware modeling, particularly the parallelism of hardware, in a mainstream programming language.

An important objective was that software engineers should be comfortable with using SystemC. Rather than invent a new language, SystemC is based on the existing C++ language. SystemC is a true super-set of C++, so any C++ program is automatically a valid SystemC program.

SystemC uses the template, macro and library features of C++ to extend the language. The key features it provides are:

A C++ class, sc_module, suitable for

defining hardware modules containing parallel

processes

![[Note]](./images/note.png) | Note |

|---|---|

Process is a general term in SystemC to describe the various ways of representing parallel flows of control. It has nothing to do with processes in the Linux or Microsoft Windows operating systems. |

A mechanism to define functions modeling the parallel

threads of control within sc_module

classes;

Two classes, sc_port and

sc_export to represent points of

connection to and from a sc_module;

A class, sc_interface to describe the

software services required by a sc_port

or provided by a sc_export;

A class, sc_prim_channel to represent the

channel connecting ports;

A set of derived classes, of

sc_prim_channel,

sc_interface,

sc_port and

sc_export to represent and connect common

channel types used in hardware design such as signals, buffers and

FIFOs; and

A comprehensive set of types to represent data in both 2-state and 4-state logic.

The full specification is 441 pages long [5]. The OSCI reference distribution includes a very useful introductory user guide and tutorial [7].

To understand transaction level modeling, it is essential to understand the difference in approach to parallelism taken in hardware and software design.

A hardware engineer, typically writing in a

Hardware Description Language (HDL)

such as Verilog or VHDL, describes a design as a collection of

parallel activities, which communicate via shared data. The parallel

activities are always (Verilog) or

process (VHDL) blocks. The shared data structures

are wires or signals.

This follows very naturally the way that physical hardware behaves. There is no one flow of control—all parallel components are active at the same time, with their individual flow of control.

By contrast, a software engineer typically describes parallelism in a design as a number of threads, which pass flow of control between them. The threads communicate by a number of mechanisms (message passing or remote procedure call for example), but although there is logical parallelism, only one thread is ever physically active at one time.

This follows naturally the behavior on a conventional uni-processor CPU, where there is a single program counter indicating the next instruction to execute, and so only one flow of control. Even with modern multiprocessors, this is still a natural way of programming for the software engineer, because the number or threads or processes will often exceed the number of processor cores available.

A simple way to model hardware is via a round-robin, which updates the state of each component as time advances. Each component is represented as a software function. A master clock function calls each component function in turn when the clock advances—for example on each clock edge. The wires between the components are represented as variables shared between the components. A number of tools (e.g. ARC VTOC, ARM RealView SoC Designer, Carbon SpeedCompiler, Verilator) use this approach to cycle accurate modeling.

With its close parallel of the way hardware is designed with languages such as Verilog and VHDL, this approach has merit for detailed modeling. It is well suited to cycle accurate modeling where every hardware register and wire must be accurate.

Efficiency demands that not every HDL process or

always is built as a separate function. Automated

tools which generate cycle accurate models in SystemC from HDL can

often reduce complex designs to a small number of functions executed

on each cycle.

For less detailed models, the overhead in calling each component whenever time advances cannot be justified.

The solution is to model each component only when it has something to do. The individual components communicate by sending messages requesting data be transferred between each other. The exchange of messages is called a transaction, and the approach Transaction Level Modeling (TLM).

This mirrors the way hardware behaves at the high level, where functional blocks communicate by reading and writing across buses.

OSCI TLM 2.0 offers a standard approach to building Transaction Level Models.

At the simplest level a TLM is a set of SystemC modules (i.e. C++ classes), each providing one or more sockets through which the SystemC modules may read and write data.

The behavior of each module is provided by a number of parallel threads (functions of the C++ class), which communicate with the threads in other modules by passing data (i.e. reading or writing) through the sockets. This communication is known as a transaction and the data passed as a payload. Figure 2.1 shows the key components in a TLM 2.0 model.

The data passed in a transaction may take any form. However the TLM 2.0 standard defines a generic payload which is suitable for many uses, and which can be extended if required. By using the generic payload, a TLM 2.0 model will maximize interoperability.

The main features of the generic payload are:

Is this a read or a write?

What is the address (in the hardware sense of an address in memory).

A pointer to the physical data as an array of bytes

A pointer to an array indicating which bytes of the data are valid.

An indication of whether the transaction was successful, and if not the nature of the error.

Further features provide support for streaming, custom memory management and extensions to the generic payload.

A TLM 2.0 transport function is used to pass the payload to another SystemC thread and obtain a response—i.e. a transaction.

The generic payload is suitable for modeling a wide range of bus interfaces and protocols. However where additional features are required, TLM 2.0 provides an extension mechanism. The chapter on implementing a transactional JTAG debugger interface (see Chapter 11) describes the use of this extension mechanism to model the data for a bit-serial interface.

A module's threads may act as either initiators or targets. An initiator is responsible for creating a payload (see Section 2.3.1) and calling the transport function to send it. A target receives payloads from the transport function for processing and response. In the case of non-blocking interfaces (see Section 2.3.3), the target may create new transactions backwards in response to a transaction from an initiator.

Initiator calls are made through initiator sockets, target calls received through target sockets. A module may implement both target and initiator sockets, allowing its threads to both generate and receive traffic.

There are two principal types of TLM 2.0 transport function.

The blocking transport functions are called by the initiator thread, received by the target thread, which processes the request and then returns the result. Until the transaction has been processed and released the initiator thread is blocked.

The non-blocking transport functions are called by the initiator thread, received by the target thread, which immediately returns, before processing the request. Subsequently the target, having processed the request makes a transport call backwards to the initiator to return the result.

In the non-blocking case there are actually two types of transport used. The forward transport path is used by the initiator to pass the request to the target and the backward transport path used by the target to return the response. The advantage of the non-blocking transport interface is that the initiator can carry on processing, while the target is processing the request originally made.

In addition TLM 2.0 provides two more specialized types of transaction.

A debug transaction is a read that does not affect the state of the model. These are for use by debuggers, which wish to see the state of a model, without affecting that state.

TLM 2.0 recognizes that a full-blown transaction is too heavyweight for some types of access. For example an ISS accessing memory using transactions would destroy performance. TLM 2.0 provides the concept of a direct memory interface, allowing threads direct access to blocks of memory in other threads for high performance.

TLM 2.0 considers two levels of timing detail.

A loosely timed model uses transactions corresponding to a complete read or write across a bus or network in physical hardware. It provides timing at the level of the individual transaction.

An approximately timed model breaks down transactions into a number of phases corresponding much more closely to the phasing of particular hardware protocols (for example the address and data phases of an AHB read or write).

Typically loosely timed models are implemented with a blocking interface and approximately timed models with a non-blocking interface.

TLM 2.0 also introduces the concept of temporal decoupling. Standard SystemC keeps a single synchronized view of time, which is used by all threads in all modules. However with temporal decoupling, each thread can keep its own local view of time, allowing the thread to run ahead in simulation time, until it needs to synchronize with another thread. This improves performance in loosely timed models with blocking interfaces, by avoiding bottlenecks in processing.

To ensure that one thread doesn't run away hogging all the processing, TLM 2.0 temporal decoupling uses the concept of the quantum, the greatest amount that a thread may differ in timing from the central view of time. This allows other threads a chance to catch up

TLM 2.0 does not have an explicit concept of an untimed socket (something that was explicit in TLM 1.0). The standardization group took the view that in practice all models need some concept of time, so purely untimed models are of little value.

However, untimed models are easily implemented as loosely timed models which always set the timing parameter in transport calls to zero. The example in Chapter 4, Chapter 6 and Chapter 7 uses this approach to create an untimed model. This is then refined in Chapter 8 to add synchronous timing information and in Chapter 9 to add temporal decoupling.

The standard TLM 2.0 approach to modeling requires the user to derive their own classes from the standard TLM 2.0 sockets, so that those sockets can then implement the TLM 2.0 interfaces. Modules then instantiate these derived sockets and use the bind function to connect them to sockets on other modules.

This is a very flexible approach, but the need to define new derived classes for sockets is an unnecessary layer of complexity for simple modeling. For such uses, the TLM 2.0 standard defines a number of convenience sockets which can be instantiated directly by modules, and which specify their interface functions as callbacks.

These convenience sockets are used throughout the case study in this application note.

[1] There are some exceptions, most notably Simula67, one the languages which inspired C++. In some respects it is remarkably like SystemC.

In this case study, TLM 2.0 convenience sockets are used to wrap an existing ISS. This is then built into a simple SoC using additional hand-written TLM 2.0 components.

Modeling uses the TLM 2.0 generic payload with no extensions. It is independent of the specific bus architecture that will be used in the implementation.

The ISS used is from the OpenCores (www.opencores.org) project. This open source project has developed a complete 32/64-bit architecture, the OpenRISC 1000, complete with GNU compiler chain, architectural simulator and Linux port. This application note uses the OpenRISC 1000 architectural simulator, Or1ksim as the ISS for all the examples.

The model is constructed in a number of stages:

The basic wrapper for the Or1ksim ISS is built using TLM 2.0 convenience sockets and tested with a simple logger. In this first stage timing is ignored—this is effectively an untimed model. See Chapter 4 and Chapter 5.

A model UART is added as an example peripheral, demonstrating how TLM 2.0 and existing SystemC technologies can be mixed. See Chapter 6.

A model of a terminal is added as a test bench for the SoC. This demonstrates how to add SystemC components which use operating system I/O without blocking the SystemC thread. See Chapter 7.

Synchronous timing is added to each component, making the model loosely timed. See Chapter 8.

Temporal decoupling is added to the Or1ksim ISS, UART and terminal, to improve the performance of the model. See Chapter 9.

Interrupt modeling is added to the UART and the Or1ksim ISS, allowing the model to run Linux. See Chapter 10.

A second thread, modeling the JTAG interface to the processor is added to the wrapper. This demonstrates how the ISS wrapper can be multi-threaded, while the underlying OpenRISC 1000 ISS remains single threaded. This interface allows the model to be driven from a debugger such as GDB. See Chapter 11.

Simple applications, compiled with the OpenRISC 1000 tool chain are used throughout to exercise the model components. The final model is demonstrated booting a Linux 2.6 kernel.

The example, a simple SoC, is based on the Or1ksim ISS for the OpenRISC 1000 architecture. The OpenRISC 1000 architecture is a conventional 32-bit DSP/RISC design, with optional caches and MMU. Or1ksim is an interpreting ISS written in C, which in its standard configuration models main memory and a number of peripherals as well as the CPU itself.

A key feature of Or1ksim is that it is single threaded and the code is generally not re-entrant. Much of the challenge in wrapping such an ISS is ensuring consistency within a multi-threaded SystemC environment.

Information on obtaining and setting up the open source Or1ksim simulator and its tool chain are given in Embecosm Application Note 2. The OpenCores OpenRISC 1000 Simulator and Tool Chain: Installation Guide. [4].

For Chapter 4 through Chapter 9 the Or1ksim ISS is configured to model only the CPU and main memory, with example peripherals modeled as separate SystemC modules. For Chapter 10, the ISS is configured to model the data and instruction MMUs and a programmable interrupt controller (PIC). This allows the ISS to support interrupt driven peripherals and hence Linux

In Chapter 11 a second thread is introduced to the wrapper to model the JTAG debugging interface. This allows the model to be run under the control of a debugger such as GDB

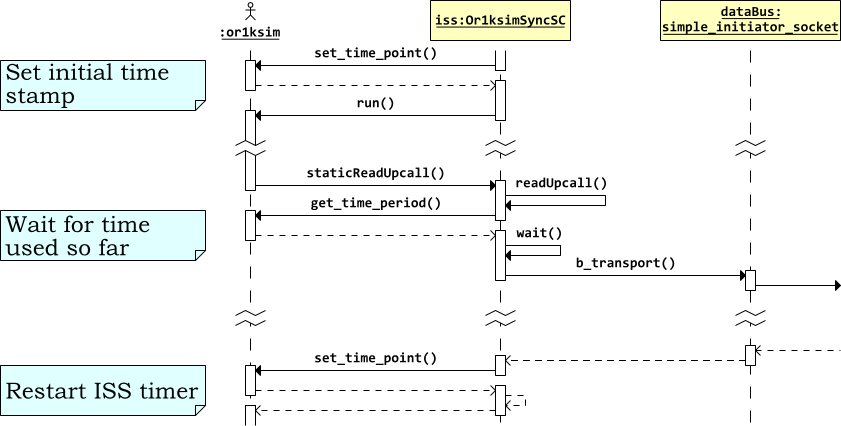

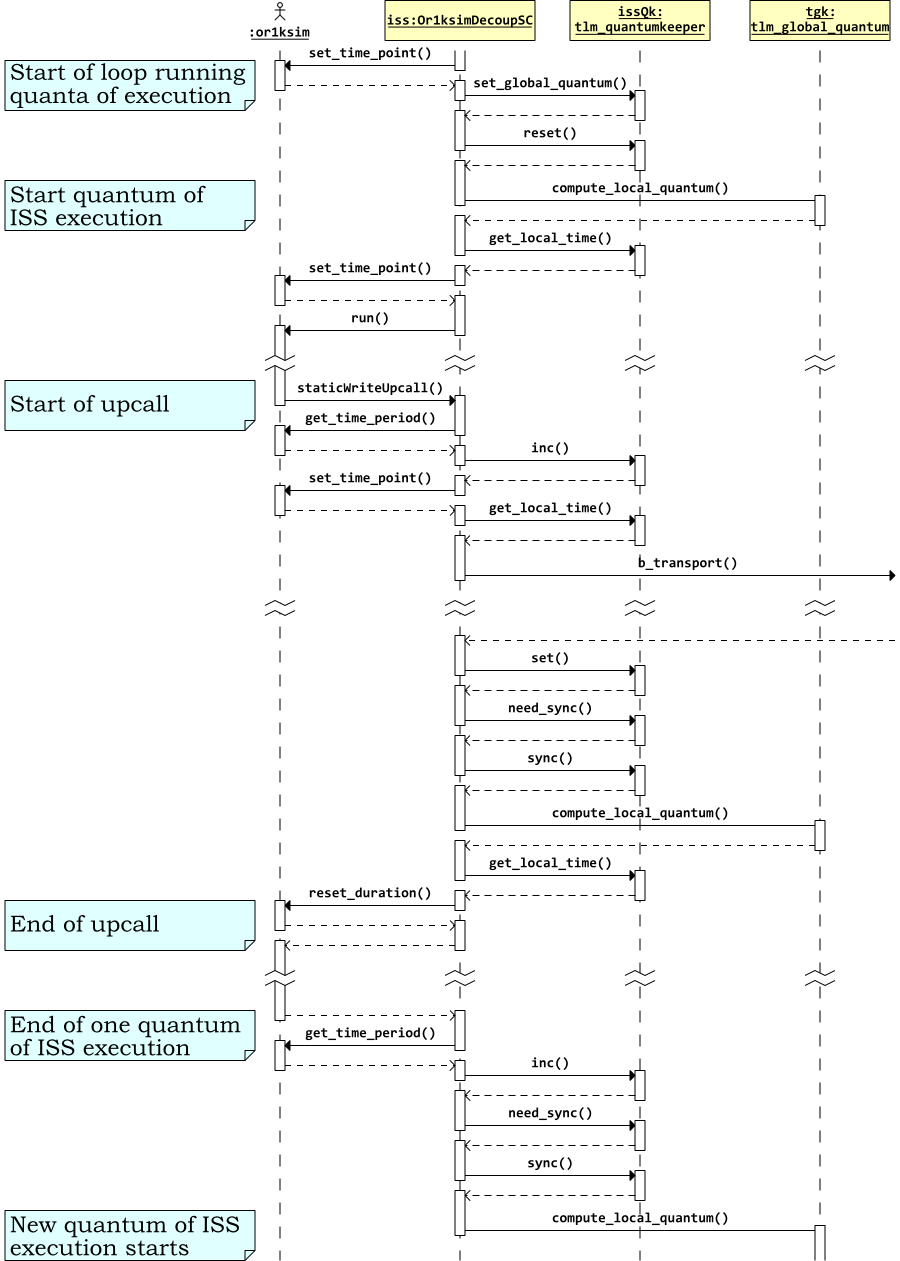

In Chapter 4 the TLM 2.0 wrapper for the Or1ksim ISS is developed. In Chapter 5 the wrapped ISS is tested by connection to a simple TLM 2.0 logger module. This module records transactions sent to it on standard output as shown in Figure 3.1.

To build a simple SoC the Or1ksim ISS CPU/memory subsystem is connected to a UART modeled in SystemC using TLM 2.0. The test bench for the system is a terminal, also modeled in SystemC using TLM 2.0 as shown in Figure 3.2. The model is built up in stages starting with the ISS wrapper module developed in Chapter 4. In Chapter 6 and Chapter 7 models of the UART and terminal are added to create an untimed model. Synchronous timing to create a loosely timed model is added in Chapter 8 and temporal decoupling to improve performance is added in Chapter 9. .

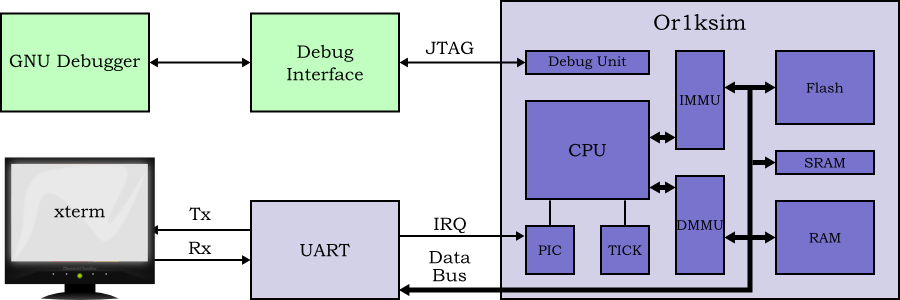

To run Linux (see Chapter 10), the example must be extended to support interrupt driver I/O. It also needs memory management and other peripheral functions. This is provided internally to the Or1ksim ISS. This design is shown in Figure 3.3.

A software debugger typically interacts with a processor via an independent debugging interface. For the OpenRISC 1000 the debug interface uses IEEE 1149.1 JTAG. To allow the debugger to connect to the model we must model this interface. This design is shown in Figure 3.4.

The code of the distribution is organized as follows.

configure

The main configuration script.

linux.cfg

An Or1ksim configuration file for use when running Linux.

progs-or32

A collection of OpenRISC 1000 programs which run on the models created. Binaries are provided as well as source, but to recompile the example programs requires the OpenRISC 1000 tool chain. See Embecosm Application Note 2. The OpenCores OpenRISC 1000 Simulator and Tool Chain: Installation Guide. [4] for more information on building the OpenRISC 1000 tool chain.

simple.cfg

An Or1ksim configuration file for use when running simple examples.

sysc-models

The SystemC code for the various models. A separate directory is provided for each model. In each case the models build on previous models using the C++ class inheritance mechanism.

logger

The simplest model, providing a base class wrapper to Or1ksim and connecting to a simple logger class, which can check the correct behavior of the bus. See Chapter 4 and Chapter 5.

simple-soc

The simplest complete SoC model, adding a UART and

terminal emulator to the Or1ksim model. The base

Or1ksim wrapper class from logger

is extended to allow other threads to execute. See Chapter 6 and Chapter 7.

sync-soc

This extends the SoC wrapper from

simple-soc to add synchronized

timing. Derived classes of the UART and terminal

emulator also add synchronized timing. See Chapter 8.

decoup-soc

Decoupled timing is added to the SoC wrapper from

sync-soc. A decoupled version of

the UART is also implemented. See Chapter 9.

intr-soc

This is a version of the SoC wrapper from

decoup-soc which adds interrupt

handling. A version of the UART which supports

interrupt based operation is also implemented. This

allows Linux to be supported. See Chapter 10.

jtag-soc

The SoC wrapper from intr-soc is

extended with an additional thread implementing a JTAG

interface. This allows code running on the model to be

debugged using a tool such as GDB. See Chapter 11.

uml

UML design information for all the models, created with BoUML is provided in this directory.

Various other files and directories are included. These form part of the standard GNU autotools infrastructure.

The code throughout is documented with

Doxygen (see www.doxygen.org). This provides

a description of the code, generated automatically from the

source. The generated HTML can be found in the

doc/html sub-directory of both the SystemC

model directory and the OpenRISC 1000 program directory.

All the examples in this application note separate the definition of

a class (i.e. what it does) in a

.h file, from the implementation

(i.e. how it does it) in a

.cpp file. Class X is

defined in file X.hX.cpp

The examples use the convention that classes and other type names

start with an Upper Case letter

(e.g. Or1ksimSC), variables and functions

start with a lower case letter (e.g. dataBus) and

defined or enumerated constants are all in UPPER CASE

(e.g. #define BAUD_RATE 9600). All SystemC

module classes end with the characters 'SC'.

C++ provides the hierarchical class mechanism, where

derived classes inherit (some) of the

functions and variables of their

base class. This feature is heavily used

within SystemC—for example all module classes are derived

classes of the SystemC base class,

sc_module.

The SystemC models in each section of this application note are built using derived classes of the models from previous sections.

Those functions and variables which other classes will use are

declared as public. For SystemC modules this

usually means the constructor and any SystemC ports or

sockets. Occasionally there are some utility functions which are

also made public (see for example

Or1ksimExt::isLittleEndian in Section 6.3)[2].

Variables and functions in classes that are not for use by other

classes, but are required in derived classes are declared as

protected (i.e. visible to derived classes).

The remaining functions and variables, which are for use only by the

current class, are declared private (visible only

to this class). This avoids any unplanned reuse by derived classes.

Some of the functions will be reimplemented in later derived

classes. Such functions are also declared virtual.

In summary public functions and variables may be

used by any other class, protected functions and

variables may be used only by this class and

any derived classes and private functions and

variables may be used only by this class. virtual

functions may be reimplemented in derived

classes.

The entire example system is now built using the GNU; autotools. This provides for flexibility in configuration and building of the system.

![[Note]](./images/note.png) | Note |

|---|---|

This is a major change since issue 1 of this application note. |

Full details of how to configure and build the models are in Appendix A.

[2]

Object oriented purists prefer to expose only class functions as

the public interface, so hiding all state

implementation from external view. There is considerable merit

in this, but the common SystemC convention is to expose actual

ports or sockets, rather than accessor functions for those

objects. This application note follows this practice.

The conversion of an existing ISS to a SystemC module with TLM 2.0 sockets involves several steps.

Modify the existing ISS (in this example Or1ksim written in C) so it behaves in a manner suitable for wrapping (see Section 4.1).

Define a SystemC module for the wrapper (see Section 4.2) and provide its implementation (see Section 4.3).

Test the wrapper with a simple logger module attached to the TLM 2.0 socket and a suitable test application running as embedded code on the ISS (see Chapter 5).

The code for the Or1ksim wrapper module

(Or1ksimSC.cpp and

Or1ksimSC.h) may be found in the

sysc-models/logger directory of the distribution.

Most ISS need some modification before they can be incorporated into a TLM 2.0 framework. Like many ISS, Or1ksim is designed as a standalone program. The options are:

Given the choice, option 2 is more flexible, making the ISS widely reusable in other environments. It is the approach adopted in this application note.

It is not intended that the reader should have to understand the internal workings of Or1ksim. All the changes described in this application note form part of Or1ksim 0.4.0.

With the exception of the examples in Chapter 11, the changes described in this application note also form part of Or1ksim 0.3.0.

Details of obtaining Or1ksim are provided in Appendix A.

The Or1ksim main function first initializes

the ISS, then sits in a loop executing instructions. This

main function is replaced by a series of

functions which form the interface to the library. The interface

functions needed are:

int or1ksim_init (const char *config_file,

const char *image_file,

void *class_ptr,

int (*upr) (void *class_ptr,

unsigned long int addr,

unsigned char mask[],

unsigned char rdata[],

int data_len),

int (*upw) (void *class_ptr,

unsigned long int addr,

unsigned char mask[],

unsigned char wdata[],

int data_len));

or1ksim_init initializes the

simulator. For Or1ksim, configuration data is read from a

file, which is passed as the first argument,

config_file. The program image is passed as

a second argument, image_file.

Or1ksim also needs to be able to call up to the SystemC

model of which it is part—to read and write from the

peripheral address space. These are provided as the fourth

and fifth arguments, upr and

upw. More explanation of the upcall

mechanism can be found in Section 4.2.6.

Function calls between C and C++ can be awkward. The upcall

functions form part of the SystemC module object, but are

written as static functions with C linkage. To enable these

functions to invoke functions in the SystemC module, they are

passed a pointer to the module class instance to use as a

handle. This pointer forms the third argument,

class_ptr.

int or1ksim_run( double duration );

or1ksim_run runs the simulator for the

specified time in seconds.

These functions are a standard part of the Or1ksim 0.3.0 and Or1ksim 0.4.0 libraries.

The standard Or1ksim ISS incorporates the functionality of several common peripherals. The objective of this application note is to demonstrate the ISS driving external peripherals modeled in SystemC using TLM 2.0 interfaces.

Or1ksim peripherals are configured in a textual configuration

file, with a section (introduced by the keyword

section) for each device attached. This

configuration file specifies the memory mapped addresses of the

peripheral. Any reads or writes to those addresses will be directed

to the code of the peripheral within Or1ksim.

Or1ksim is extended with a new class of peripheral,

generic, which specifies an external

peripheral. The specification in the configuration file specifies

the memory mapped address range covered and whether byte, half word

or full word access are enabled. Multiple generic

sections may be defined (for different address ranges) in the

configuration file.

Code is added to Or1ksim, so that any read or write to a

generic peripheral is redirected back to the

wrapper code via the upcalls specified as arguments to

or1ksim_init (see Section 4.1.1 and Section 4.2.6).

The class definition for the Or1ksim ISS wrapper module may be

found in the file sysc_models/logger/Or1ksimSC.h.

The Or1ksim SystemC wrapper module class,

Or1ksimSC, is defined in the file

Or1ksimSC.h. It will provide a single initiator

socket, for data access, dataBus. No instruction

accesses are planned, so modeling an external instruction bus is

unnecessary.

The module includes the tlm.h header, which

defines the core TLM 2.0 interface and the required convenience

wrapper header—in this case for a simple initiator socket.

The POSIX stdint.h header is also included, since

the definitions and code will make use of the fixed width native

types defined there.

#include <stdint.h> #include "tlm.h" #include "tlm_utils/simple_initiator_socket.h" #include "or1ksim.h"

![[Note]](./images/note.png) | Note |

|---|---|

There is no need to include the standard

|

The module is declared as a standard SystemC module, i.e. as a

derived class of sc_core::sc_module.

class Or1ksimSC

: public sc_core::sc_module

{

![[Note]](./images/note.png) | Note |

|---|---|

SystemC provides a macro, so that a module can be defined by: SC_MODULE( Or1ksimSC ) However this is equivalent (IEEE 1666-2005 section 5.2.5) to the C++ derived class declaration

class Or1ksimSC

: public sc_core::sc_module

{

public:

By using

The examples provided with SystemC and TLM 2.0 all use explicit

declarations of classes derived from

|

Or1ksimSC needs a custom constructor, which

can be passed the Or1ksim ISS configuration and image files. It

will call the or1ksim_init function within the

Or1ksim library (see Section 4.1.1) to

initialize the ISS.

Or1ksimSC( sc_core::sc_module_name name,

const char *configFile,

const char *imageFile );

The default destructor is sufficient here. The module has no tidying up to do on termination.

The only public interface is the TLM 2.0 simple initiator convenience

socket, dataBus. The TLM 2.0 convenience sockets are

templated with

the class of which any callbacks are members;

a bus width (default BUSWIDTH, 32); and

a protocol type (default the TLM 2.0 base protocol types).

For this case study, the default bus width and protocol are

appropriate and need not be specified. There is no default class for

the template, so Or1ksimSC is used. A class must be

specified, even where (as in this case for a simple blocking

initiator) no callbacks are actually required.

tlm_utils::simple_initiator_socket<Or1ksimSC> dataBus;

The module has a single thread, which executes the instructions of

the ISS. The run function implements this:

void run();

The thread is not part of the public interface, but will but will be

reused and reimplemented in derived classes later in the application

note, so it is declared protected and

virtual.

The Or1ksim ISS makes requests to read and write peripherals via

the upcalls passed as arguments to or1ksim_init

(see Section 4.1.1).

The Or1ksim ISS is implemented in C, which cannot easily call

C++ class instance functions. The solution is to declare two

static member functions which can be called

from C. The call to or1ksim_init also received

the address of the actual C++ class instance (cast to

void *). This pointer is passed back with

the upcall, so the static function can call the corresponding

instance function.

A total of 4 functions are needed, one static and one instance each for read and write. The static functions use the native C/C++ types (unsigned long int), but convert to defined fixed width types for the instance functions. The native SystemC 64-bit unsigned type is used for the address (which is always 64 bits in TLM 2.0 function calls) and the POSIX 32-bit unsigned data type is used for the byte enable mask and data.

These upcall functions are not changed throughout this application note, so are declared private.

static int staticReadUpcall (void *instancePtr,

unsigned long int addr,

unsigned char mask[],

unsigned char rdata[],

int dataLen);

static int staticWriteUpcall (void *instancePtr,

unsigned long int addr,

unsigned char mask[],

unsigned char wdata[],

int dataLen);

int readUpcall (unsigned long int addr,

unsigned char mask[],

unsigned char rdata[],

int dataLen);

int writeUpcall (unsigned long int addr,

unsigned char mask[],

unsigned char wdata[],

int dataLen);

![[Caution]](./images/caution.png) | Caution |

|---|---|

It might seem logical to use the SystemC limited precision types, rather than the POSIX types. However the SystemC types are not native C++ types, so will not cast as expected. |

The transport mechanism is common to both, so provided in a utility

function, doTrans. This function will be used

and re-implemented in derived classes, so is declared

protected and virtual.

When invoked, each upcall will need to populate a new payload. Since this is something local in both scope and extent to the upcall and its lifetime, the instinct is to declare it as an automatic variable within each upcall.

However the TLM 2.0 generic payload has a large underlying structure and complex initialization, so such a local declaration carries a significant performance penalty if it is constructed each time the upcall is used.

Since only one upcall is ever in use at any one time, we can declare the payload as a class instance variable. Since it is only used by the upcalls, it can be private to this class.

tlm::tlm_generic_payload trans;

![[Note]](./images/note.png) | Note |

|---|---|

The performance overhead in instantiating a generic payload is not mentioned in the TLM 2.0 LRM. I am indebted to Robert Günzel for bringing the issue to my attention. |

The class implementation for Or1ksimSC may be

found found in sysc-modules/logger/Or1ksimSC.cpp

in the distribution.

All the definitions required are obtained from the definition file:

#include "Or1ksimSC.h"

The implementation of a C++ class that is a SystemC module with

SystemC threads (SC_THREAD), methods

(SC_METHOD) or clocked threads

(SC_CTHREAD) requires a number of definitions for

that class to be set up using the SC_HAS_PROCESS

macro.

SC_HAS_PROCESS( Or1ksimSC );

![[Caution]](./images/caution.png) | Caution |

|---|---|

The

The

In cases such as this, where the constructor implementation is

separate from the definition, SystemC requires that the

|

The constructor passes the name to the constructors of its base

class (sc_module) and its simple initiator socket

(dataBus), then calls the

or1ksim_init function in the Or1ksim library

to initialize the ISS.

The member function, run is associated with the

class as a SystemC thread, using the SC_THREAD

macro. It will be called automatically by the SystemC kernel after

elaboration (i.e SystemC initialization).

Or1ksimSC::Or1ksimSC ( sc_core::sc_module_name name,

const char *configFile,

const char *imageFile ) :

sc_module( name ),

dataIni( "data_initiator" )

{

or1ksim_init( configFile, imageFile, this, staticReadUpcall,

staticWriteUpcall );

SC_THREAD( run ); // Thread to run the ISS

} /* Or1ksimSC() */

The main thread, run, invokes the Or1ksim

ISS to run for ever (by passing a negative time argument). The ISS

will use the upcalls (see Section 4.2.6) to request

reads from and writes to the peripheral address space.

The thread is called automatically when the SystemC kernel has completed elaboration (i.e. is initialized).

void

Or1ksimSC::run()

{

scLastUpTime = sc_core::sc_time_stamp();

or1kLastUpTime = or1ksim_time();

(void)or1ksim_run( -1.0 );

} // Or1ksimSC()

Two functions are declared as static member functions to implement the upcalls from the Or1ksim library (see Section 4.2.6 for an explanation of why these functions are static).

The static functions receive the pointer to the

Or1ksimSC instance which originally started the

Or1ksim ISS (provided as an argument to

or1ksim_init described in Section 4.3.3).

This allows each static function to call the instance function which

implements the upcall, as shown here with

staticReadUpcall:

int

Or1ksimSC::staticReadUpcall (void *instancePtr,

unsigned long int addr,

unsigned char mask[],

unsigned char rdata[],

int dataLen)

{

Or1ksimSC *classPtr = (Or1ksimSC *) instancePtr;

return classPtr->readUpcall (addr, mask, rdata, dataLen);

} // staticReadUpcall()

The instancePtr argument allows identification of

the particular instance of the class which called

or1ksim_run and hence to which the upcall is

directed. The remaining arguments are passed to the instance method

unchanged.

![[Caution]](./images/caution.png) | Caution |

|---|---|

It might be thought that providing a direct upcall to the C++

upcall functions of the class would be more efficient, using the C++

member reference operator ( Linkage to static functions is much simpler and usually works between C and C++. So the approach used here is more reliable. |

The upcalls from the ISS generate the transactional activity. These functions set up the payload, execute the transaction (i.e exchange the payload and result with the target) and return the result to the ISS.

The example here is coded in a very simple fashion, in the knowledge

that the requests to read are always four bytes long (the OpenRISC 1000 has

a simple 32 bit bus), possibly with some bytes masked out for byte

and half-word reads. This matches the default

BUSWIDTH of the simple initiator socket.

As noted in Section 4.2.6, the payload is declared as a class instance variable, rather than locally here for performance reasons. This has the added benefit that it will also work should we ever convert the model to using a non-blocking socket, where the lifetime of the payload would need to be longer than the lifetime of the upcall. TLM 2.0 requires that the payload, data and mask fields all remain valid for the duration of the complete transaction.

Once the payload fields are set up, the

doTrans function (which is used for both read

and write) is called to transport the payload to the target and

return the result.

The transport function requires a time to be supplied, even when timing is not being used (as in this case). This must be time variable, not a constant, since the target can update the value. A dummy variable is declared with zero time and passed to the blocking transport function of the socket with the payload.

sc_core::sc_time dummyDelay = sc_core::SC_ZERO_TIME; dataBus->b_transport( trans, dummyDelay );

This implementation is sufficient for modeling just the Or1ksim

ISS in SystemC. However at no time does the thread execute a

SystemC wait call. In the absence of any such

yield, no other thread would be able to execute. This will be remedied

in Chapter 6 when other threads are added to model

peripherals.

The test configuration was shown earlier in Figure 3.1. For this a simple logger is needed, which must implement a TLM 2.0 simple target socket.

In addition, a simple embedded application is needed to run on the Or1ksim ISS, which will make reads and writes to peripheral address space, which can be detected by the logger.

All the behavior is in the callback function—there are no SystemC

threads. This means the logger will be suitable for testing the

Or1ksimSC wrapper module, even though its thread

never yields (see Section 4.3.5).

The code for the logger module (LoggerSC.cpp and

LoggerSC.h) and the main program

(loggerMainSC.cpp may be found with the Or1ksim

wrapper code in the sysc-models/logger directory of

the distribution.

The key aspects of the overall program are captured in a UML class diagram and a UML sequence diagram, showing how a read transaction is processed.

The overall class diagram for the design is shown in Figure 5.1. The Or1ksim wrapper class creates its own TLM 2.0 convenience initiator port, with which a TLM 2.0 generic payload will be associated to carry traffic. Conversely the logger class creates its own TLM 2.0 convenience target port through which it will receive the associated payload. The class structure of the underlying SystemC TLM 2.0 environment connecting initiator and target ports is not shown.

A sequence diagram, illustrating the handling of a read transaction

for the design is shown in Figure 5.2. The Or1ksim wrapper class invokes the underlying Or1ksim

ISS through its run function.

The run function executes without further

interruption. Whenever it needs to read or write via the external

bus, it uses the staticReadUpcall or

staticWriteUpcall function. This in turn

invokes the readUpcall function for the wrapper

instance.

The various TLM 2.0 generic payload functions are used to set up the

payload, before the payload is passed to the initiator port using

its b_transport function (for simplicity the

call to do_trans is omitted from the

diagram). The packet is passed internally to the connected target

port, where it invokes the handler function

(loggerReadWrite) to handle the payload. The

payload is modified as appropriate before being returned to the

initiator.

![[Note]](./images/note.png) | Note |

|---|---|

All the actions in this diagram are synchronous. There is a single thread of control, which flows from the wrapper module to the logger module as a transaction is processed. |

The code for the logger module definition may be found in

sysc-models/logger/LoggerSC.h in the

distribution.

The logger is based on the TLM 2.0 convenience simple target socket, so needs the appropriate header, in addition to the standard TLM 2.0 header:

#include "tlm.h" #include "tlm_utils/simple_target_socket.h"

The class is a standard SystemC module:

class LoggerSC : public sc_core::sc_module

A custom constructor is needed, which will be used to register the callback function for the simple target convenience socket blocking transport.

LoggerSC( sc_core::sc_module_name name );

The public interface is the single simple target convenience socket.

tlm_utils::simple_target_socket<LoggerSC> loggerPort;

The code for the logger module implementation may be found in

sysc-models/logger/LoggerSC.cpp in the

distribution.

The logger will be doing a certain amount of stream IO, so includes the C++ headers that define stream manipulation functions. The POSIX standard integer types are also included.

#include <iostream> #include <iomanip> #include <stdint.h> #include "LoggerSC.h"

The constructor passes its argument (the module) name to the base

class sc_module constructor. The body of the

function then registers the loggerReadWrite

function as the callback for blocking transport to this convenience

socket. This means that any initiator which requests blocking

transport (by calling the initiator socket's

b_transport function) will invoke this callback

function in the target.

LoggerSC::LoggerSC( sc_core::sc_module_name name ) :

sc_module( name )

{

loggerPort.register_b_transport( this, &LoggerSC::loggerReadWrite );

} // Or1ksimSC()

The callback function, loggerReadWrite records

the key information regarding any transaction it receives. The

payload is a TLM 2.0 generic payload, with appropriate access

functions. In this simple implementation, a length of 4 bytes is

assumed for the data in the payload.

To get at the data and byte enable mask, the pointers to

unsigned char are cast to pointers to the POSIX

fixed width type, uint32_t, as was used with

Or1ksimSC. Endianness issues due to the byte

pointers not being word aligned are not an issue, because the

Or1ksimSC module also declared them as

uint32_t.

void

LoggerSC::loggerReadWrite( tlm::tlm_generic_payload &payload,

sc_core::sc_time &delay )

{

// Break out the address, mask and data pointer.

tlm::tlm_command comm = payload.get_command();

sc_dt::uint64 addr = payload.get_address();

unsigned char *maskPtr = payload.get_byte_enable_ptr();

unsigned char *dataPtr = payload.get_data_ptr();

// Record the payload fields (data only if it's a write)

const char *commStr;

switch( comm ) {

case tlm::TLM_READ_COMMAND: commStr = "Read"; break;

case tlm::TLM_WRITE_COMMAND: commStr = "Write"; break;

case tlm::TLM_IGNORE_COMMAND: commStr = "Ignore"; break;

}

std::cout << "Logging" << std::endl;

std::cout << " Command: " << commStr << std::endl;

std::cout << " Address: 0x" << std::setw( 8 ) << std::setfill( '0' )

<<std::hex << (uint64_t)addr << std::endl;

std::cout << " Byte enables: 0x" << std::setw( 8 ) << std::setfill( '0' )

<<std::hex << *((uint32_t *)maskPtr) << std::endl;

if( tlm::TLM_WRITE_COMMAND == comm ) {

std::cout << " Data: 0x" << std::setw( 8 ) << std::setfill( '0' )

<<std::hex << *((uint32_t *)dataPtr) << std::endl;

}

std::cout << std::endl;

payload.set_response_status( tlm::TLM_OK_RESPONSE ); // Always OK

} // loggerReadWrite()

The logger module and the Or1ksim wrapper module must be connected

in the main program (sc_main since this is

SystemC), and the simulation invoked.

The code for the main program may be found in

sysc-models/logger/loggerMainSC.cpp in the

distribution.

The program includes the C++ iostream header,

main TLM 2.0 header and the header of the two modules which will be

used:

#include <iostream> #include "tlm.h" #include "Or1ksimSC.h" #include "LoggerSC.h"

The two iostream entities used are brought

into the local namespace.

using std::cerr; using std::endl;

The program takes two arguments, an Or1ksim configuration file (described further in Section 5.6) and a binary image to execute on the Or1ksim ISS (see Section 5.5).

int sc_main( int argc,

char *argv[] )

{

if( argc != 3 ) {

cerr << "Usage: TestSC <config_file> <image_file>" << endl;

exit( 1 );

}

Instances of the Or1ksim ISS and the logger are created, the ISS being passed the two program arguments for its initialization.

Or1ksimSC iss( "or1ksim", argv[1], argv[2] ); LoggerSC logger( "logger" );

The target socket of the logger (loggerPort) is

connected by passing it as argument to the initiator socket of the

ISS (dataBus). The C++ function application

operator, (), is overloaded for initiator sockets

to provide this binding function.

iss.dataBus( logger.loggerPort );

The test program in progs-or32/logger-test.c

defines a memory mapped volatile data structure and then writes to and

reads from each element of that structure.

The source code for the logger test program may be found in

progs-or32/logger-test.c in the distribution. It

uses the utility functions (progs-or32/utils.c

and progs-or32/utils.h) and the bootloader

(progs-or32/start.s).

The test program uses some simple utility functions which can write

characters (simputc), string

(simputs) and hexadecimal numbers

(simputh). Its header is included:

#include "utils.h"

The utilities' implementation can be found in

utils.c.

The memory mapped address is defined in the configuration of Or1ksim (see Section 5.6) to be 0x90000000. This is set as a defined constant in the test program.

#define BASEADDR 0x90000000

The memory mapped structure consists of a byte, half word (16 bits)

and full word (32 bits), all declared as volatile

within the struct. These are all declared with

the C types, which for the OpenRISC 1000 tool chain are known to correspond

to these sizes.

struct testdev

{

volatile unsigned char byte;

volatile unsigned short int halfword;

volatile unsigned long int fullword;

};

The main program declares a pointer to this

struct at the BASEADDR, along

with 3 variables to hold the results of the various sized results

when reading.

main()

{

struct testdev *dev = (struct testdev *)BASEADDR;

unsigned char byteRes;

unsigned short int halfwordRes;

unsigned long int fullwordRes;

The details of each write are logged and the value then written. (In

the absence of a printf, the logging is

necessarily cumbersome).

simputs( "Writing byte 0xa5 to address 0x" ); simputh( (unsigned long int)(&(dev->byte)) ); simputs( "\n" ); dev->byte = 0xa5; simputs( "Writing half word 0xbeef to address 0x" ); simputh( (unsigned long int)(&(dev->halfword)) ); simputs( "\n" ); dev->halfword = 0xbeef; simputs( "Writing full word 0xdeadbeef to address 0x" ); simputh( (unsigned long int)(&(dev->fullword)) ); simputs( "\n" ); dev->fullword = 0xdeadbeef;

The values are then read back. No results are expected (the logger does not set any values), but this should check the process behaves as expected.

byteRes = dev->byte; simputs( "Read 0x" ); simputh( byteRes ); simputs( " from address 0x" ); simputh( (unsigned long int)(&(dev->byte)) ); simputs( "\n" ); halfwordRes = dev->halfword; simputs( "Read 0x" ); simputh( halfwordRes ); simputs( " from address 0x" ); simputh( (unsigned long int)(&(dev->halfword)) ); simputs( "\n" ); fullwordRes = dev->fullword; simputs( "Read 0x" ); simputh( fullwordRes ); simputs( " from address 0x" ); simputh( (unsigned long int)(&(dev->fullword)) ); simputs( "\n" );

At the end of the program, the utility

simexit is used. This not only terminates the

program, but will also exit the simulation.

The program is compiled as part of the overall make and will be

found in the progs-or32 sub-directory of the

main build directory. A custom linker script ensures the program is

loaded with its bootloader at the correct address, with its entry

point at the OpenRISC 1000 reset vector (0x100).

The complete program is compiled from the top level make file. Both a

standalone program (logger) and a

libtool compliant library

(liblogger.la) are created. The library

provides a convenient mechanism for reusing the code from this

model, when creating subsequent models which use derived classes.

The SystemC modules are all compiled with

SC_INCLUDE_DYNAMIC_PROCESSES defined when

using TLM 2.0. This is a requirement for using the TLM 2.0

library. The final executable is linked against the SystemC

library.

The Or1ksim ISS is configured using a textual configuration

file, described in more detail in

Embecosm Application Note 2. The OpenCores OpenRISC 1000 Simulator and

Tool Chain: Installation Guide.

[4]. For the modified Or1ksim ISS, generic

peripherals can be added (see Section 4.1.2), which will cause code to call

out via the upcall mechanism to the Or1ksim SystemC wrapper

module (see Section 4.2.6).

The Or1ksim configuration file for this example is in

simple.cfg. It disables all the standard

peripherals and specifies one block of memory from address 0x0. It

adds a generic peripheral allowing byte, half

word and full word access to addresses mapped from 0x90000000 to

0x90000007, with the following configuration file entry

section generic enabled = 1 baseaddr = 0x90000000 size = 0x8 name = "External UART" byte_enabled = 1 hw_enabled = 1 word_enabled = 1 end

The compiled program can be executed by passing in as arguments the Or1ksim configuration file and the OpenRISC 1000 binary. The result is shown in Figure 5.3.

$ ./sysc-models/logger/logger ../simple.cfg progs-or32/logger-test

SystemC 2.2.0 --- May 16 2008 10:30:46

Copyright (c) 1996-2006 by all Contributors

ALL RIGHTS RESERVED

... <Or1ksim initialization messages>

Writing byte 0xa5 to address 0x090000000

Logging

Command: Write

Address: 0x90000000

Byte enables: 0x000000ff

Data: 0x003f54a5

Writing half word 0xbeef to address 0x090000002

Logging

Command: Write

Address: 0x90000000

Byte enables: 0xffff0000

Data: 0xefbe8fc4

... <More test program output>

Read half word 0x0FFFF from address 0x090000002

Logging

Command: Read

Address: 0x90000004

Byte enables: 0xffffffff

Read full word 0x028372F09 from address 0x090000004

exit(0)

@reset : cycles 0, insn #0

@exit : cycles 33297, insn #16581

diff : cycles 33297, insn #16581

$

Figure 5.3. Output from the logger test of the Or1ksim wrapper module.

Each access from the application program generates the expected transactional access. All accesses are 32 bits wide, but for byte and half-word access the relevant bytes are masked off. The reads return meaningless values (the logger was not designed to package a return value), but in each case the value returned fits in the size requested as expected.

![[Note]](./images/note.png) | Note |

|---|---|

The Or1ksim ISS can be configured to model little-endian architectures. The TLM 2.0 payloads are always packed with data using the endianness of the model. If the exercise were repeated with a little-endian version of Or1ksim the addresses of the access would be unchanged (they are word aligned), but the byte enable masks for the byte and half word accesses would be inverted. |

This example uses a single peripheral, a UART. The UART model is based on National Semiconductor 16450 design. The Or1ksim ISS wrapper must be extended to work with this UART.

The code for the UART module (UartSC.cpp and

UartSC.h) may be found with the extended Or1ksim

wrapper code (Or1ksimExtSC.cpp and

Or1ksimExtSC.h) in the

sysc-models/simple-soc directory of the

distribution.

The 16450 UART is a very long established industry component. Data written a byte at a time into the transmit buffer is converted to serial pulses on the output (Tx) pin. Serial pulses on the input (Rx) pin are recognized and converted to byte values, which can be read from the receive buffer. Typically Rx and Tx are connected to a terminal and keyboard which can generate and recognize the pulses of data. The UART can also generate additional signals for terminals and keyboards to provide physical flow control, but that is beyond the scope of this model. The key interfaces are shown in Figure 6.1.

The 16450 UART specifies a set of registers which control the UART behavior. On the Tx/Rx side, this includes setting the board rate and the pattern of stop, start and data bits. On the CPU side this includes configuring interrupt behavior (if any) and setting flags to show the status of transmit and receive buffers. The registers are shown in Table 6.1.

| Address | Register | R/W | Description |

|---|---|---|---|

| 0 |

RXBUF

| R |

When the |

TXBUF

| W |

When the | |

DLL

| R/W |

When the | |

| 1 |

IER

| R/W |

The interrupt enable register. The lower 4 bits control which events generate an interrupt. |

DLH

| R/W |

When the | |

| 2 |

IIR

| R |

Interrupt identification register. Bit 0 indicates if an interrupt is pending, bits 1-2 the reason for the interrupt. |

| 3 |

LCR

| R/W |

Line control register. Various bits controlling the behavior

of the UART. Of these, |

| 4 |

MCR

| W |

Modem control register. Bits 0-4 control the behavior of the modem. |

| 5 |

LSR

| R |

Line status register. Bits 0-6 report the status of the

UART. Of these, DR, bit 0, receiver data ready is

important, indicating there is valid data in

|

| 6 |

MSR

| R |

Modem Status Register. Bits reporting the state of the modem. |

| 7 |

SCR

| R/W |

Scratch register. Not used by the UART, but may be used by the application to store an 8-bit value. |

Table 6.1. NS 16450 UART Registers

A transaction level model cannot show all the intricacies of a UART—the whole point is to simplify and remove detail.

The TLM should allow the CPU to read and write registers and communicate with a model terminal/keyboard which will send and receive characters and generate interrupts as appropriate. While all writable registers can be written and all readable registers read, only those registers and bits of registers which are relevant to this level of modeling will have any impact on behavior.

A TLM 2.0 socket is the natural model for the bus interface to the

CPU. However the interface to the terminal is much simpler.

Standard byte wide SystemC buffers

(sc_buffer) will be suitable, one for the Rx

direction and one for Tx. The buffer is implemented for the Rx

direction and a port to a buffer for the Tx direction. The terminal

(see Chapter 7) will offer the complementary

arrangement.

![[Note]](./images/note.png) | Note |

|---|---|

A SystemC buffer ( |

The interrupt is not modeled as an interface at this stage, so the UART will only be suitable for polled use. An interrupt interface is added in Chapter 10.

The divisor latch affects the baud rate, which will affect timing of transfers. This will be covered in a later section (see Chapter 8), but is not needed for the current untimed model. The value can be written and read, but does not affect behavior.

All interrupts are modeled (see Section 6.2.3), so all bits in the interrupt enable and interrupt control register are modeled.

The modem control and status registers are only modeled to the extent of supporting modem loopback. This is used by some software to determine the nature of the modem (for example in the standard Linux serial line driver).

The line control register sets details of the bit transfers. In a later section (see Chapter 8), this will affect the timing of transfers, but it is not relevant to the current untimed model.

In the Line Status Register, the Data Ready and

Transmitter Holding Empty/Transmitter

Empty bits are the only ones modeled. The model does not

distinguish a separate buffer and holding transmit register, so the

last two of these will move in step in the model.

For a larger system, the Or1ksim wrapper module described in Chapter 4 must be extended. A public function is required for peripheral models to establish the CPU endianness.

The function must be added to the underlying Or1ksim library and

then a wrapper function added to the Or1ksimSC

wrapper module.

In Section 4.3.5 it was noted that the

absence of any call to wait meant the Or1ksim

ISS could be the only thread in the model. The

doTrans function must be extended to yield

after each transaction to allow other threads to run. For our new

model, this would prevent the UART and terminal models from running.

These extensions are achieved by defining a new

class, Or1ksimExtSC derived from the existing

Or1ksimSC class. It inherits all the

functionality of the existing class, re-implements that of the transport

function, doTrans and adds an additional public

interface function, isLittleEndian.

The additional function is straightforward, since endianness is a compile time constant in the Or1ksim ISS.

int or1ksim_is_le();

or1ksim_is_le returns 1 if Or1ksim is

modeling a little endian

architecture, 0 otherwise. It is needed to ensure the payload is

packed with the correct byte ordering.

This function is a standard part of the Or1ksim 0.3.0 and Or1ksim 0.4.0 libraries.

The new class, Or1ksimExtSC is derived from

Or1ksimSC, so the definition file includes

its header. The module class can then inherit from that class.

#include "Or1ksimSC.h"

class Or1ksimExtSC

: public Or1ksimSC

{

A custom constructor must be defined. Custom constructors do not inherit, so a new custom constructor is defined just to pass the arguments on to the base class.

Or1ksimExtSC( sc_core::sc_module_name name,

const char *configFile,

const char *imageFile );

A new public function to report the endianness of the underlying CPU model is defined

bool isLittleEndian();

The doTrans function is reimplemented here, to

allow the thread to yield. The function remains protected and

virtual, since it will be redefined again later in this application

note.

virtual void doTrans( tlm::tlm_generic_payload &trans );

The extended Or1ksim wrapper module class,

Or1ksimExtSC, definition may be found in

sys-models/simple-soc/Or1ksimExtSC.h in the

distribution. It uses the TLM 2.0 simple target convenience socket

(described earlier in Chapter 5).

The constructor just passes its arguments to its base class

Or1ksimExtSC::Or1ksimExtSC ( sc_core::sc_module_name name,

const char *configFile,

const char *imageFile ) :

Or1ksimSC( name, configFile, imageFile )

{

} // Or1ksimExtSC()

isLittleEndian is a simple wrapper for the

underlying Or1ksim ISS library function[3].

bool

Or1ksimExtSC::isLittleEndian()

{

return (1 == or1ksim_is_le());

} // or1ksimIsLe()

The majority of the code for doTrans is

unchanged from its implementation in

Or1ksimSC. The addition is a

wait for zero time immediately after the

transaction has completed. This allows the SystemC thread to

yield, so that any other threads that are ready can take a turn.

wait( sc_core::SC_ZERO_TIME );

![[Caution]](./images/caution.png) | Caution |

|---|---|

The call to The implementation currently is untimed, so a zero delay wait is perfectly acceptable. That just gives all the other untimed threads a turn at execution.

The logger described in Chapter 5

worked without this call to |

The extended Or1ksim wrapper module class,

Or1ksimExtSC implementation may be found in

sys-models/simple-soc/Or1ksimExtSC.cpp in the

distribution.

[3]

A technicality is that the Or1ksim library function,

is_little_endian returns an

int, since C does not have a

bool type. A C++ compiler would automatically

convert one to the other, but making the comparison explicit is

good for clarity. The same code will be generated, so there is

no loss of performance.

The UART module class, UartSC definition may

be found in sys-models/simple-soc/UartSC.h in the

distribution. It uses the TLM 2.0 simple target convenience socket

(described earlier in Chapter 5).

The header files for TLM 2.0 and the simple target convenience socket are included.

#include "tlm.h" #include "tlm_utils/simple_target_socket.h"

Convenience constants for the address mask, named register offsets and bit fields are then defined. The address mask is needed, since in this simple SoC model there is no arbiter/decoder to strip out the higher order bits from the address before the transaction is sent to the UART.

#define UART_ADDR_MASK 7 // Mask for addresses (3 bit bus)

Named constants are defined giving the address offset of each register of the UART

#define UART_BUF 0 // R/W: Rx/Tx buffer, DLAB=0 #define UART_IER 1 // R/W: Interrupt Enable Register, DLAB=0 #define UART_IIR 2 // R: Interrupt ID Register #define UART_LCR 3 // R/W: Line Control Register #define UART_MCR 4 // W: Modem Control Register #define UART_LSR 5 // R: Line Status Register #define UART_MSR 6 // R: Modem Status Register #define UART_SCR 7 // R/W: Scratch Register

Bit masks are declared for each of the bits and bit fields of interest in the UART. For example the interrupt identification register needs a mask for the pending bit of a mask for the two bits representing the highest priority interrupt and a mask for each possible interrupt.

#define UART_IIR_IPEND 0x01 // Interrupt pending (active low) #define UART_IIR_MASK 0x06 // the IIR status bits #define UART_IIR_RLS 0x06 // Receiver line status #define UART_IIR_RDA 0x04 // Receiver data available #define UART_IIR_THRE 0x02 // Transmitter holding reg empty #define UART_IIR_MOD 0x00 // Modem status

The main class is a standard SystemC module class derived from

sc_core::sc_module.

class UartSC

: public sc_core::sc_module

{

The module has a customized constructor, specifying an input clock rate (which in the SoC example will be the SoC clock rate), and a flag to indicate the endianness of the model.

UartSC( sc_core::sc_module_name name,

unsigned long int _clockRate,

bool _isLittleEndian );

The interfaces to the UART model are:

The simple target convenience socket, bus,

representing the bus from the CPU;

A byte wide SystemC buffer

(sc_buffer<unsigned char>) for

the Rx pin; and

A byte wide SystemC output port

(sc_out<unsigned char>) for

the Tx pin.

No external port is provided for the interrupt at this stage. That will be added in Chapter 10

A SystemC thread, busThread, is provided to

handle transactions arriving on the bus. A SystemC method,

statically sensitive to writes to the Rx buffer is used to handle

bytes arriving in the Rx buffer.

![[Note]](./images/note.png) | Note |

|---|---|

Unlike threads, SystemC methods may not yield by calling

it is worth using SystemC methods whenever possible, because they can potentially be implemented more efficiently than threads. |

The blocking transport callback function is

busReadWrite. This in turn calls for two

separate functions which implement read specific

(busRead) and write specific

(busWrite) behavior.

A utility function, modemLoopback determines

the state of registers and generates an interrupt in the event of

modem loopback being requested (a bit in the modem control

register). It is used by the busRead and

busWrite functions.

Three utility functions are provided to handle

interrupts. setIntrFlags sets the interrupt

indication register according to which interrupts are currently

pending. genIntr generates an interrupt and

clrIntr clears an interrupt. In this

implementation these functions ensure all register flags are set

correctly but do not drive an external interrupt signal.

A set of convenience utilities are provided to set and clear flags

in registers (set and

clear) and to test the state of a flag bit in a

register (isSet and

isClear).

struct regs is used to hold

the value of each register. There are ten of these, since register

0 is really two registers, depending on whether it is being read

(rbr) or written (thr) and the

divisor latch is really an extra 16 bit register.

struct {

unsigned char rbr; // R: Rx buffer,

unsigned char thr; // R: Tx hold reg,

unsigned char ier; // R/W: Interrupt Enable Register

unsigned char iir; // R: Interrupt ID Register

unsigned char lcr; // R/W: Line Control Register

unsigned char mcr; // W: Modem Control Register

unsigned char lsr; // R: Line Status Register

unsigned char msr; // R: Modem Status Register

unsigned char scr; // R/W: Scratch Register

unsigned short int dl; // R/W: Divisor Latch

} regs;

An additional register, intrPending, holds flags

(corresponding to the interrupt enable register bits) indicating which

interrupts are currently pending. A flag initialized at construction

records the model endianness, isLittleEndian.

A function is needed for the TLM 2.0 callback function,

busReadWrite to notify the thread handling

data being sent for transmission

(busThread). This is achieved with a

SystemC event:

sc_core::sc_event txReceived;

The callback function notifies on this event, to trigger behavior in

the busThread.

The UART module class, UartSC implementation

may be found in sys-models/simple-soc/UartSC.cpp

in the distribution.

Implementation of the constructor is preceded, like

Or1ksimSC, by the SystemC macro.

SC_HAS_PROCESS( UartSC );

The constructor calls the base class

(sc_module) constructor to set the module

name, saves the endianness flag in its internal state variable and

clears the interrupt pending flags. The thread to handle bus I/O is

associated with this module.

SC_THREAD( busThread );

The method handling data on the Rx buffer is associated with this module with static sensitivity to writes to that buffer. It is not initialized.

SC_METHOD( rxMethod ); sensitive << rx; dont_initialize();

The blocking transport callback is registered for the

bus socket, in the same manner as was used for

the logger, LoggerSC.

bus.register_b_transport( this, &UartSC::busReadWrite );

Finally the registers (regs) are cleared.

We use the term processes in the SystemC

sense to cover both SC_THREAD and

SC_METHOD.

The busThread is a

SC_THREAD. It sits in a perpetual loop. It first

marks the transmit buffer as empty (on reset the flags are cleared,

so the buffer will appear full).

![[Note]](./images/note.png) | Note |

|---|---|

The 16450 UART describes two flags for transmit buffer status, one to indicate that the transmit holding register is empty and a second to indicate that the internal transmit buffer register is empty. For simplicity, this model does not model a separate internal register (effectively a one byte FIFO), so both flags are set and cleared together. |

If the transmit buffer empty interrupt is enabled, the thread generates an interrupt to indicate that the buffer is empty.

The thread then waits until it is notified via the SystemC event

txReceived that a byte is in the buffer to be

sent. This event will be triggered by the

busWrite callback when a value is written into

the transmit holding register.

![[Note]](./images/note.png) | Note |

|---|---|

It might be thought that a SystemC

That would certainly be suitable in this implementation. However

this is a virtual function, and when we reimplement later to add

timing, we will wish to call |

The second process, rxMethod is a SystemC

SC_METHOD, sensitive to characters appearing in

the Rx buffer. The character is read into the read buffer register

and the line status data ready flag is set to indicate availability.

If the receive data interrupt is enabled, an interrupt is asserted to indicate data availability.

The registered callback function is busReadWrite,

which breaks out the address, byte enable mask pointer and data

pointer. A switch statement on the mask is used

to determine the offset of the actual byte requested and hence the

exact byte address, allowing for the endianness of the model. This

also provides a check that only a single byte is being requested.

switch( *((uint32_t *)maskPtr) ) {

case 0x000000ff: offset = isLittleEndian ? 0 : 3; break;

case 0x0000ff00: offset = isLittleEndian ? 1 : 2; break;

case 0x00ff0000: offset = isLittleEndian ? 2 : 1; break;

case 0xff000000: offset = isLittleEndian ? 3 : 0; break;

default: // Invalid request

payload.set_response_status( tlm::TLM_GENERIC_ERROR_RESPONSE );

return;

}

In a perfect world, the router/arbiter function would have masked

the address to the range handled by the UART. However for this

simple model, the full address is received, so masking with

UART_ADDR_MASK is carried out here, to give the

address of the UART register being read.

Separate functions, busRead and

busWrite are used to implement the register

specific behavior, selected as appropriate based on the payload

command field.

Single byte reads and writes always succeed, so the response is set

to tlm::TLM_OK_RESPONSE in all cases.

Read behavior is handled by busRead. A

switch on the address is used to identify the result to be returned,

usually just the value in the register if it is readable. The

interesting cases are:

If the DLAB bit is set in the line control

register, then reads to the first two registers (read buffer and

interrupt enable) yield instead the low and high bytes of the

divisor latch.

Reading the read buffer (when DLAB=0) yields

the byte just read, if flag DR is set in the

line status register. The act of reading causes the

DR flag and the read buffer full interrupt to

be cleared. If no interrupts remain pending then the interrupt

pending flag is cleared.

Reading the interrupt indicator register clears the transmit buffer empty interrupt if it was pending. If no interrupts remain pending, then the interrupt pending flag is cleared.

Reading the line status register clears any error indications and the receive line status interrupt if it was pending, although the model has no way of setting any of these indications. If no interrupts remain pending, then the interrupt pending flag is cleared.

Reading the modem status register clears all flags and the modem

status interrupt if it was pending. However the modem loopback

indication may still be in operation and if so the bits and

interrupts are set to indicate the state of the loopback by a

call to modemloopback. If no interrupts

remain pending, then the interrupt pending flag is cleared.

Write behavior is handled by busWrite. A

switch on the address is used to identify the action

required. Usually the register is just written (if writable). The

interesting cases are: